Application Note

June 1998

AN9816

## Introduction

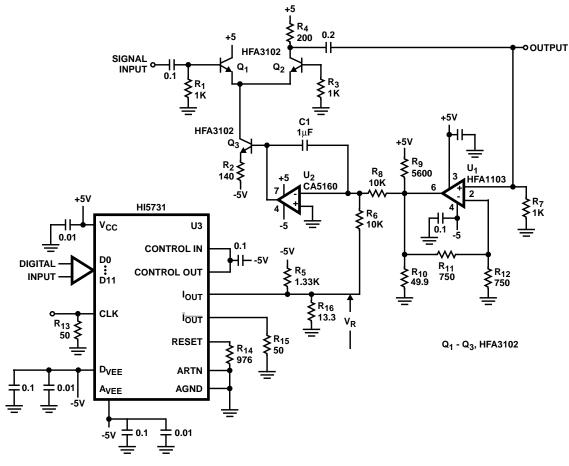

Many systems (especially communications) require an AGC which will function at 50MHz. Self-calibrating systems such as automatic test equipment also need the high frequency response, but they add a requirement that the AGC output voltage be set by a digital signal. During the calibration cycle this test equipment will calculate the AGC output voltage needed to achieve the accuracy requirements, and they will increment the AGC output voltage until the system is within specifications. The AGC circuit described in Figure 1 uses a DAC to accomplish the digital control, and because the DAC is the reference input for the AGC circuit, it ultimately sets the AGC output voltage. The HI5731 was chosen for the DAC because it is inexpensive, it functions with 5V supplies, the output interfaces well with the AGC circuit, and it can be updated at a 100MHz rate. The heart of the AGC circuit is a variable gain amplifier made from a three transistor, longtailed pair configuration, Q1, Q2, and Q3. When the base voltage of Q<sub>3</sub> is varied the emitter current of the long-tailed pair changes, forcing a gain change according to the following equation, where K is a function of the emitter current and V<sub>B3</sub> is the base voltage of Q<sub>3</sub>:

$G = KV_{IN}|V_{B3}|$ (EQ. 1)

The gain-control and bias-stability parameters of the circuit depend on the transistor matching, so the circuit uses a HFA3102-matched, long tailed array for Q<sub>1</sub> through Q<sub>3</sub>. The usable range of V<sub>B3</sub> is -0.04 to -4.1V, which corresponds to a gain range of 0.8 to 17.6dB, respectively (V<sub>IN</sub> = 100mV). This gain span is a total of 16.8dB. The gain is proportional to R<sub>4</sub>. Increasing R<sub>4</sub> increases the gain, but the gain span stays constant at approximately 16.8dB while the frequency response decreases.

The gain span limits the AGC circuit's ability to compensate for input voltage changes greater than the gain span, 16.8dB. If the input voltage change will exceed the gain span it can be almost doubled by putting two long-tailed pair in series; this is aided by the HFA3102 because it contains two long-tailed pairs. AC connect the collectors of the first stage differently to the bases of the second stage. Connecting the bases of the current source transistors in parallel enables the AGC circuit to maintain the same control function, while the gains of the two long-tailed pairs are multiplied thus, essentially doubling the gain span.

The input signal is amplified by the long-tailed pair to make the gained up output signal, which in turn is half-wave rectified by the HFA1103 to produce a quasi DC control voltage. The HFA1103 is a high speed op amp that has the lower half of the output stage disconnected, so because the output can't go below ground it make a fine half wave rectifier or sync stripper. R<sub>9</sub>, through R<sub>12</sub> set the gain to two, and add a few mV of bias to ensure that the output is always positive. This DC voltage is compared with the DAC output voltage in the input stage of the CA5160 integrator. Because the integrator has a large DC gain it's output voltage will swing to any point within the supplies in an attempt to lock the loop. The DAC output sinks current from ground. R<sub>5</sub> and R<sub>16</sub> form a voltage divider with DC offset, and this DC voltage, which is the reference input, V<sub>R</sub>, for the AGC circuit, is compared with the output of  $U_1$  in the integrator,  $U_2$ .

The signal path has excellent frequency response because the HFA3102 is the only component in the signal path. The control path through  $U_1$  does not have quite as good a frequency response, so  $R_4$  or the input signal must be increased to provide control past 50MHz. The DAC transfers the digital input to an internal register on the rising edge of the clock pulses. The circuit uses the non-inverting DAC output to yield a positive-increasing transfer function, but you can obtain the inverse-transfer function by using the inverting DAC output (Table 1).

|          | AGC PERFORMANCE SUMMARY   |

|----------|---------------------------|

| IADLE I. | AGC PERFORIMANCE SUMIMART |

| PARAMETER                          | МІЛІМИМ             | MAXIMUM             |

|------------------------------------|---------------------|---------------------|

| Gain (dB)                          | 0.8                 | 17.6                |

| V <sub>B3</sub> (V)                | -0.04               | -4.1                |

| V <sub>R</sub> (V)                 | -0.045              | -0.275              |

| Digital Input/Non-Inverting Output | 1111 1111 1111      | 0000 0000 0000 0000 |

| Digital Input/Inverting Output     | 0000 0000 0000 0000 | 1111 1111 1111 1111 |

Fast DAC updates will not affect the output signal with the selected value of  $C_1 = 1\mu F$  because the integrator filters out the change. When the DAC updates, the output voltage will slowly change to the new value. If the circuit is only used for system calibration where slow DAC updates are the rule, you can use a slower DAC. However, you may have to redesign

the interface circuit (U<sub>2</sub> and associated components) if the DAC output current swing changes. If the value of C<sub>1</sub> is decreased the amplitude of the output signal will tend to follow the DAC updates, thus, if the DAC updates are done in a sinusoidal manner the output signal will be amplitude modulated by the DAC update frequency.

FIGURE 1. HIGH FREQUENCY AGC HAS DIGITAL CONTROL

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site www.intersil.com